Shuang-Yuan Chen 1, Hung-Wen Chen1, Chia-Hao Tu1, Shao-Min Ho1, Lie-Chia Shie1 and Heng-Sheng Haung1

1Institute of Mechatronic Engineering, National Taipei University of Technology, Taipei, Taiwan 106, R.O.C.

Received:

December 18, 2006

Accepted:

June 8, 2007

Publication Date:

March 1, 2008

Download Citation:

||https://doi.org/10.6180/jase.2008.11.1.01

ABSTRACT

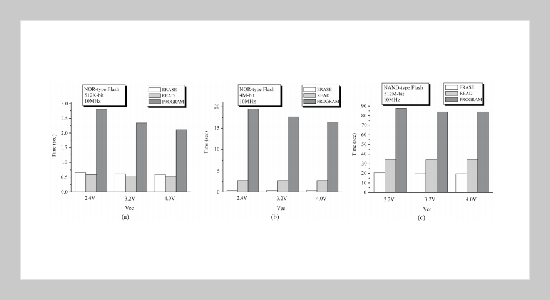

The capacity of flash memory increases rapidly due to the surging requirement of consumer electronics. This inevitably implies that the test time of these memories is becoming longer. As the test time is directly proportional to the test cost, test time reduction (TTR) has been becoming an important issue. In this paper, tuning the test voltages and frequencies of test program for TTR is presented for the first time. Each of programming, erasing and reading operations was evaluated for two types of NOR and one type of NAND flash memories. Based on the experimental results, the programming operation is the most time consuming among the three operations and can be effectively reduced by enhancing the test voltage and/or frequency. The reasons of the effectiveness are also provided. In the last, the optimal combinations of the supply voltages and test frequencies are proposed for each of the NOR and NAND-type memories.

Keywords:

Test Time Reduction, TTR, Flash Memory, Memory Testing

REFERENCES

- [1] Cappelletti, P., Golla, C., Olivo, P. and Zanoni, E., Flash Memories, Kluwer Academic Publishers, Norwell, MA, U.S.A., pp. 466479 (1993).

- [2] Yeh, J. C., Kuo, S. F., Wu, C. W., Huang, C. T. and Chen, C. H., “A Systematic Approach to Reducing Semiconductor Memory Test Time in Mass Production,” 2005 IEEE International Workshop on Memory Technology, Design, and Testing, Aug. pp. 97102 (2005).

- [3] Wang, B., Yang, J. and Ivanov, A., “Reducing Test Time of Embedded SRAMs,” 2003 International Workshop on Memory Technology, Design and Testing, July, pp. 4752 (2003).

- [4] Wu, W. J. and Tang, C. Y. “Memory Test Time Reduction by Interconnecting Test Items,” 2000 Proceedings Ninth Asian Test Symposium, Dec., pp. 4248 (2000).

- [5] Hirase, J., “Test Time Reduction through Minimum Execution of Tester-Hardware Setting Instructions,” 2001 Proceedings 10th Asian Test Symposium, Nov. pp. 173178 (2001).

- [6] Hess, C., Read, H., Ren, J., Weiland, L. H., Cheng, J., Gan, C., Karbasi, H. and Winters, S., “Test Time Reduction Methods for Yield Test Structures,” 2003 International Conference on Microelectronic Test Structures, March, pp. 6468 (2003).